50-mm-Pitch Wide Aperture Spectroscopic Photodiode Arrays Engineering Data Sheet

### **Description**

Peripheral Imaging Corporation's WSN series is family of self-scanning photodiode solid-state linear imaging arrays. These photodiode sensors employ PIC's proprietary CMOS Image Sensing Technology to integrate the sensors into a single monolithic chip. These sensors are optimally designed for applications in spectroscopy. Accordingly, these sensors contain a linear array of photodiodes with an optimized geometrical aspect ratio (50-mm aperture pitch x 2500-mm aperture width) for helping to maintain mechanical stability in spectroscopic instruments and for providing a large light-capturing ability. The family of sensors consists of photodiode arrays of various lengths, 128, 256, and 512 pixels.

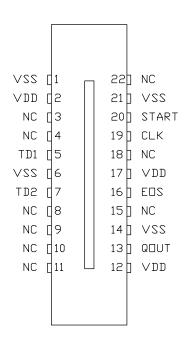

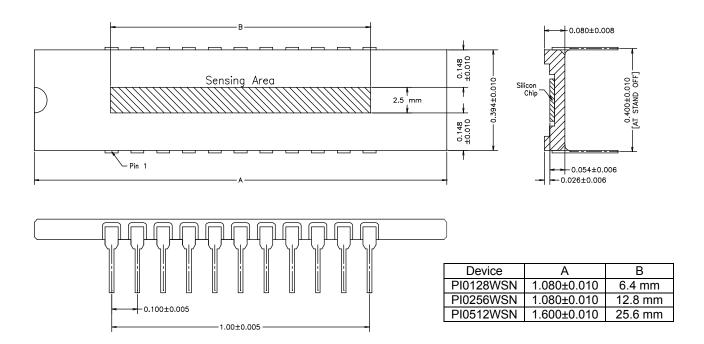

The WSN photodiode arrays are mounted in 22-pin ceramic side-brazed dual-in-line packages that fit in standard DIP sockets. A diagram of its pinout configuration is seen in Figure 1.

#### **Features**

- 65-pC saturation capacity for wide dynamic range.

- Wide spectral response (180 1000 nm) for UV and IR response.

- NP junction photodiodes with superior resistance to UV damage.

- Low dark current.

- Integration time up to 9 seconds at room temperature.

- Integration time extended to hours by cooling.

- High linearity.

- Low power dissipation (less than 1 mW).

- Geometrical structure for enhanced stability and registration.

- Standard 22-lead dual-in-line IC package.

Figure 1. Pinout configuration.

#### **Sensor Characteristics**

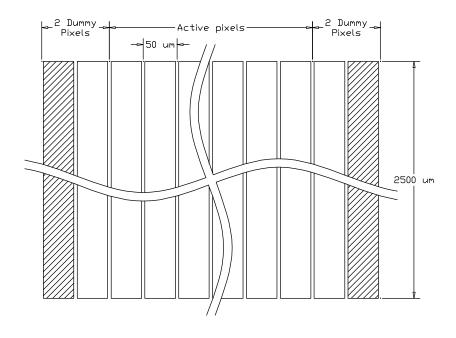

The Peripheral Imaging Corporation's self-scanned WSN photodiodes are spaced on a 50-mm pitch. The line density is 20 diodes/mm and accordingly the overall die lengths of the different arrays vary with the number of photodiodes. For example, the 128-pixel array is 6.4-mm long, the 256-pixel array is 12.8-mm long, and the 512-pixel array is 25.6-mm long. Each array has four additional dummy photodiodes. On each side, there are one dark (non-imaging) dummy photodiode and one imaging dummy photodiode. The height of the sensors is 2500 mm. The tall, narrow apertures make these sensors desirable for use in monochromators and spectrographs.

**Engineering Data Sheet**

Figure 2. Geometry and layout of photodiode pixels.

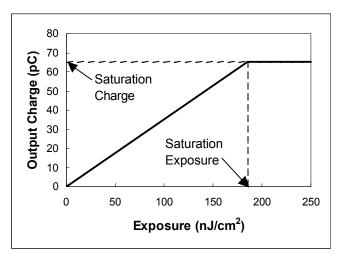

During normal operation, the photons incident in or near the NP photodiode junction generate free charges that are collected and stored on the junction's depletion capacitance. The number of collected charges is proportional to the light exposure. Figure 3 shows the stored signal charge as function of light exposure at a wavelength of 575 nm. The exposure is the product of the light intensity in nW/cm² and integration time in seconds. The charge accumulates linearly until reaching the saturation charge, and the corresponding exposure is the saturation exposure.

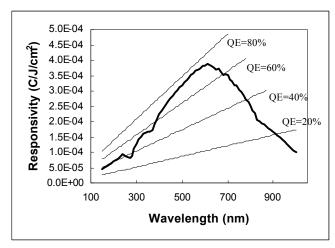

The responsivity may be calculated as the saturation charge divided by saturation exposure. The predicted typical responsivity of a photodiode is  $3.5 \times 10^{-4}$  C/J/cm<sup>2</sup> at 575 nm. Figure 4 shows the predicted responsivity of the photodiodes as a function of wavelength.

Figure 3. Stored signal charge as function of exposure at a wavelength of 575 nm.

**Engineering Data Sheet**

Figure 4. Predicted spectral response.

Note: Quantum Efficiency (QE) can be calculated by dividing the responsivity by the area of the sensor's element and multiplying the resulting ratio by the energy per photon in electron volts (eV).

The dark current is typically 0.2 pA at 25°C and varies as function of temperature. The dark current will contribute dark-signal charges and these charges will increase linearly with integration time. The dark signal and the photogenerated signal combined result in the total signal charge.

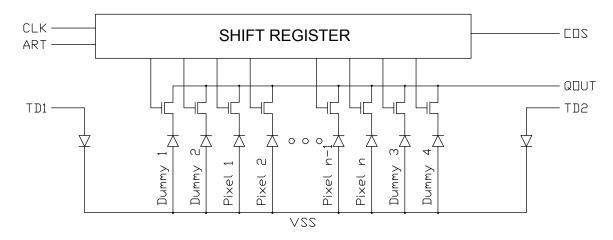

Although the WSN package has 22 pins, as shown in Figure 1, there are only 6 functionally active I/O pins in addition to the supply pins, as shown in Figure 5. In

### **Self-Scanning Circuit**

Figure 5 shows a simplified electrically equivalent circuit diagram of the photodiode array. An MOS read switch connects every photodiode in the array to a common output video line. Incident photons generate electron charge that is collected on each imaging photodiode while the switch is open. The shift register is activated by the start pulse. A pulse propagates through each shift register stage and activates the MOS read switches sequentially. As the shift register sequentially closes each read switch, the negative stored charge, which is proportional in amount to the light exposure, from the corresponding photodiode is readout onto the video line, QOUT. Typically, an external charge-integrating amplifier senses the negative output charge on the video line from each photodiode pixel. The shift register continues scanning the photodiodes in sequence, until the last shift register stage is reach, at which time the fourth and last dummy pixel is read out and end-of-scan (EOS) output is held high for one clock cycle. The next start pulse can then restart the shift register.

#### I/O Pins

essence, only two clocks, CLK and START, are required for controlling the timing of the sensor's video readout. The remaining I/O descriptions are for the

Figure 5. Simplified circuit diagram of a WSN photodiode array.

**Engineering Data Sheet**

video signal output, the end-of-scan signal, the two temperature diodes, and the supply biases. QOUT must be biased externally to Vbias (see Recommended Operating Conditions section below). Each temperature diode is operated with a small constant current that forward-biases its PN junction. By meas-

uring the forward-bias voltage, one can track the silicon die temperature. The temperature diodes may be disabled by connecting their anodes to VSS. These I/Os are listed with their acronym designators and functional descriptions in the following Table 1.

Table 1. Symbols and functions and I/O pins.

| Symbol | Function and Description                                                      |  |  |  |  |

|--------|-------------------------------------------------------------------------------|--|--|--|--|

| VSS    | Ground.                                                                       |  |  |  |  |

| VDD    | +5.0 Volts.                                                                   |  |  |  |  |

| START  | Start Pulse: Input to start the line scan.                                    |  |  |  |  |

| CLK    | Clock Pulse: Input to clock the shift register.                               |  |  |  |  |

| EOS    | End Of Scan: Output from the shift register to indicate the completion of one |  |  |  |  |

|        | line scan.                                                                    |  |  |  |  |

| QOUT   | Video Charge Output: Output from the photodiodes pixels.                      |  |  |  |  |

| TD1    | Temperature Diode 1: Anode of temperature diode 1.                            |  |  |  |  |

| TD2    | Temperature Diode 2: Anode of temperature diode 2.                            |  |  |  |  |

| NC     | No Connection                                                                 |  |  |  |  |

**Engineering Data Sheet**

### **Clock and Voltage Requirements**

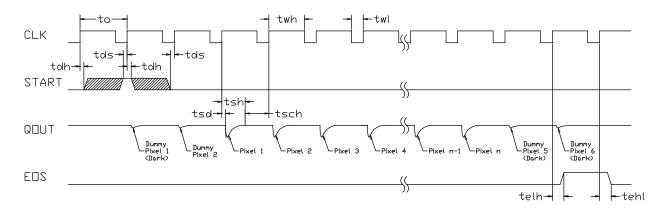

The clocking requirements are relatively simple. As it was indicated in Figure 5 and Table 1, there are only two input signals that require clocked inputs. They are CLK, the clock for the shift register, and START, the

shift register start pulse. The timing specifications and the symbol definition for Figure 6 are listed in Table 2. The control clock amplitudes for I/Os are compatible with the 5-Volt CMOS devices.

Figure 6. Timing diagram.

Table 2. Symbol definitions and timing specifications for timing diagram.

| Item                        | Symbol | Min                          | Typical | Max          | Units |

|-----------------------------|--------|------------------------------|---------|--------------|-------|

| Clock cycle time            | to     | 666 (128WSN)<br>666 (256WSN) | 10000   |              | ns    |

|                             |        | 1000 (512WSŃ)                |         |              |       |

|                             |        | 566 (128WSN)                 |         |              |       |

| Clock high pulse width      | twh    | 566 (256WSN)                 |         |              | ns    |

|                             |        | 900 (512WSN)                 |         |              |       |

| Clock low pulse width       | twl    | 100                          |         |              | ns    |

| Clock duty cycle            |        | 1                            | 50      | 99           | %     |

| Data setup time             | tds    | 100                          |         |              | ns    |

| Data hold time              | tdh    | 100                          |         |              | ns    |

| EOS low-to-high delay       | telh   |                              |         | 400          | ns    |

| EOS high-to-low delay       | tehl   |                              |         | 400          | ns    |

| Signal delay time           | tsd    | 50                           |         |              | ns    |

|                             |        |                              |         | 566 (128WSN) |       |

| Signal settling time        | tsh    |                              |         | 566 (256WSN) | ns    |

|                             |        |                              |         | 900 (512WSN) |       |

| Signal settle to clock edge | tsch   | 0                            |         |              | ns    |

**Engineering Data Sheet**

### **Recommended Operating Conditions**

The following table lists the recommended operating conditions.

Table 3. Recommended operating conditions at 25 °C.

| Parameters                        | Symbol | Min                                             | Typical   | Max                                          | Units |

|-----------------------------------|--------|-------------------------------------------------|-----------|----------------------------------------------|-------|

| Power supply                      | VDD    | 4.5                                             | 5.0       | 5.5                                          | Volts |

| Input clock pulses high level 1   | Vih    | VDD – 0.8                                       | VDD       | VDD                                          | Volts |

| Input clock pulse low level 1     | Vil    | 0.0                                             | 0.0       | 0.8                                          | Volts |

| Video charge output external bias | Vbias  | VDD – 0.5                                       | VDD – 0.5 | VDD                                          | Volts |

| Clock frequency                   | Fclk   |                                                 | 0.1       | 1.5 (128WSN)<br>1.5 (256WSN)<br>1.0 (512WSN) | MHz   |

| Integration time <sup>2</sup>     | Tint   | 0.09 (128WSN)<br>0.18 (256WSN)<br>0.52 (512WSN) |           | 9000                                         | ms    |

#### Notes:

- 1. Applies to all control-clock inputs.

- 2. Integration time is specified at room temperature such that the maximum dark current charge build up in each pixel is less than 10% of the minimum saturation charge. Accordingly, it may be as long as 9 seconds at room temperature. Longer integration times may be achieved by cooling the device. An appropriate clock frequency must be chosen so that the shift register completes its operation within the desired integration time.

**Engineering Data Sheet**

### **Electro-Optical Characteristics**

The following table lists the electro-optical characteristics.

Table 4. Electro-optical characteristics at 25 °C.

| Parameters                             | Symbol | Min | Typical               | Max | Units               |

|----------------------------------------|--------|-----|-----------------------|-----|---------------------|

| Center-to-center spacing               |        |     | 50                    |     | μm                  |

| Aperture width                         |        |     | 2500                  |     | μm                  |

| Pixel area                             | Α      |     | 1.25x10 <sup>-3</sup> |     | cm <sup>2</sup>     |

| Fill factor 1                          | FF     |     | 86                    |     | %                   |

| Quantum efficiency 1,2                 | QE     |     | 70                    |     | %                   |

| Responsivity 1,2                       | R      |     | 3.5×10 <sup>-4</sup>  |     | C/J/cm <sup>2</sup> |

| Nonuniformity of response <sup>3</sup> |        |     | 2                     | 5   | +/-%                |

| Saturation exposure <sup>2</sup>       | Esat   | 160 | 185                   |     | nJ/cm <sup>2</sup>  |

| Saturation charge <sup>4</sup>         | Qsat   | 55  | 65                    |     | рC                  |

| Average dark current 5                 |        |     | 0.2                   | 0.6 | pА                  |

| Spectral response peak                 | λ      |     | 600                   |     | nm                  |

| Spectral response range <sup>6</sup>   |        |     | 180 – 1000            |     | nm                  |

#### Notes:

- Fill factor, quantum efficiency, and responsivity are related by the equation R = (q<sub>e</sub>λ/hc) QE FF A, where q<sub>e</sub> is the charge of an electron and hc/λ is the energy of a photon at a given wavelength. Responsivity is therefore given per pixel.

- 2. At wavelength of 575 nm (yellow-green) and with no window.

- 3. Measured at 50% Vsat with an incandescent tungsten lamp filtered with an Schott KG-1 heat-absorbing filter.

- 4. Saturation charge specified for a video output bias of 4.5 volts.

- 5. Max dark leakage ≤ 1.5 x average dark leakage measured with an integration period of 500 ms at 25°C.

- 6. From 250-1000 nm, responsivity ≥ 20% of its peak value.

**Engineering Data Sheet**

### **Package Dimensions**

The following figure provides the package dimensions.

Figure 7. Package dimensions.

**Note:** Dimensions are in inches except where millimeters (mm) are indicated.

©2001-2002 AMI Semiconductor. Printed in USA. All rights reserved. Specifications are subject to change without notice. Contents may not be reproduced in whole or in part without the express prior written permission of AMIS. Information furnished herein is believed to be accurate and reliable. However, no responsibility is assumed by AMIS for its use nor for any infringement of patents or other rights granted by implication or otherwise under any patent or patent rights of AMIS.